:: AIDA Framework

- Fully automatic design or semi-automatic allowing designer intervention.

- Supported System:

Cent OS 6&7, Linux RedHatEnterprise 5&6

:: AIDA-C

- Uses standard electrical circuit simulators as evaluation engines.

- Handles multiple circuit test-benches simultaneously.

- Performs geometric and parasitic layout-aware circuit-level multi-objective multi-constraint optimization.

- Provides a Pareto optimal front of circuit sizing solutions showing the trade-offs among the design objectives.

:: AIDA-L

- Semi-automatic template generation from netlist.

- Template-based floorplanner with symmetry and automatic proximity constraints.

- Electromigration and IR-drop aware symmetric routing.

- Layout-aware circuit-level multi-objective multi-constraint optimization.

- Includes a technology independent analog module generator to enrich floorplan solutions.

Solutions

The AIDA framework implements an automatic analog IC design flow from a circuit-level specification to a physical layout description. The circuit-level synthesis is done by AIDA-C, and after the circuit-level design, AIDA-L takes the device sizes and the best floorplan, and generates the complete layout, which is then saved as a GDSII stream format.

AIDA-C is a circuit-level synthesizer supported by state-of-the-art multi-objective optimization kernels, where the robustness of the solutions is attained by considering user-defined worst case corners, that account for process variations and(or) PVT corners. The circuit's performance is measured using Spectre®, Eldo® or HSPICE® electrical circuit simulators.

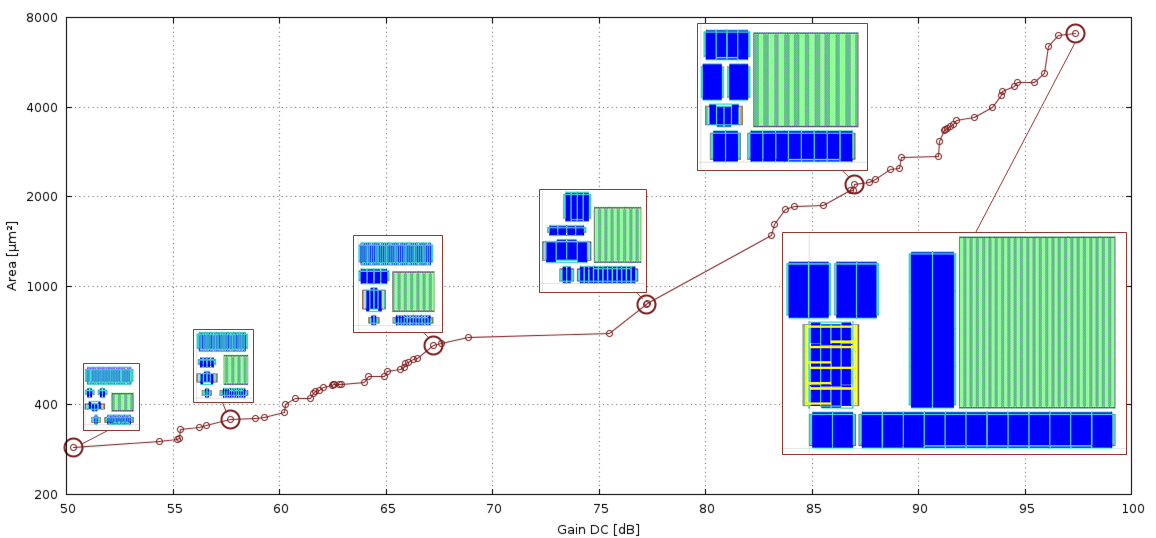

| Pareto optimal solution set for Area vs. DC Gain optimization with superimposed circuit layouts. |

|

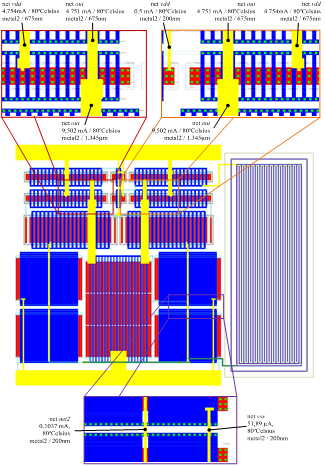

AIDA-L considers sized circuit to generate the complete layout by placing and, routing the devices, while fulfilling the technology design rules by using built-in DRC and LVS procedures. The router takes into account the circuit's currents to mitigate electromigration and IR-drop effects, and a fast but accurate PEX procedure provides parasitic estimates to be used in AIDA-C layout-aware optimization.

|

The framework's technology independent module generator, AIDA-AMG, is capable of creating several, simple and complex, device layout styles, allowing AIDA-C floorplan-aware sizing approach to explore a much wider space of solutions leading to higher quality layouts. |

|

|||

| Complete layout detailing the connections where EM effects caused wires width to increase. | ||||