:: News & Events

- AIDASoft will be at SMACD 2023 from 3 to 5 July in Madeira Island, Portugal

- AIDA awarded the Best Paper Award 2019 - Integration, the VLSI Journal

"AIDA: Layout-aware Analog Circuit-Level Sizing with In-Loop Layout Generation" - AIDA awarded at SMACD 2019

Best Paper Award Runner-Up to "Artificial Neural Networks as an Alternative for Automatic Analog IC Placement" in Lausanne. - AIDA awarded at SMACD 2018

Best paper award to "Handling the Effects of Variability and Layout Parasitics in the Automatic Synthesis of LNAs" in Prague. - AIDA awarded at SMACD 2016

Best paper award to "On-the-fly Exploration of Placement Templates for Analog IC Layout-aware Sizing Methodologies" in Lisbon. - AIDA wins at SMACD 2015

AIDA was 1st ranked in the 2015 edition of the "Design Automation Competition" . - AIDA awarded at ISCAS 2015

The paper "LC-VCO Automatic Synthesis Using Multi-Objective Evolutionary Techniques" was distinguished with the "Best Paper Award Runner-Up".

Analog Integrated Circuit Design Automation

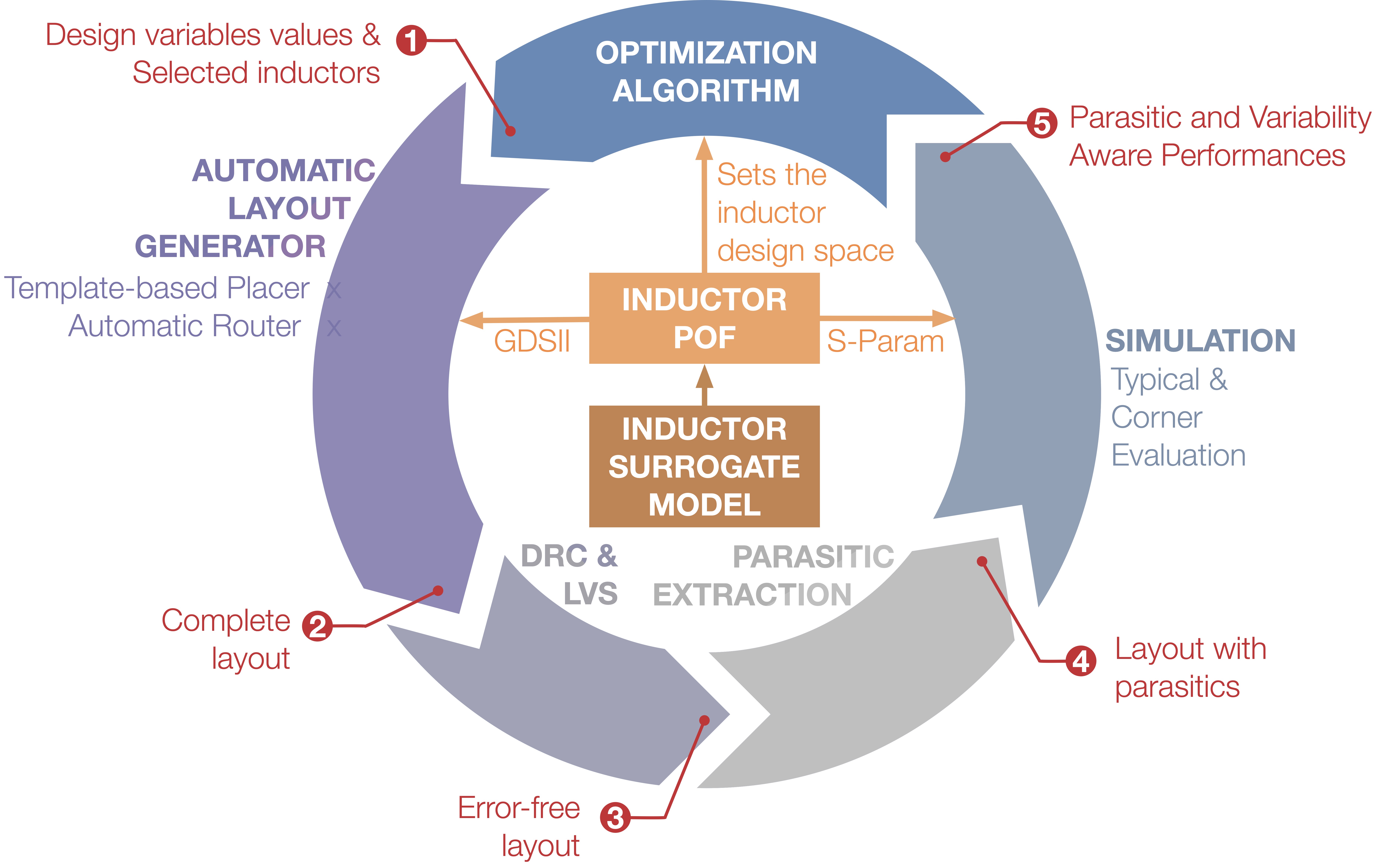

The Analog IC Design Automation (AIDA) framework implements an analog IC design flow from circuit-level specification to a physical layout description focusing on design optimizing and porting using highly efficient searching methods combined with accurate circuit-level simulation, layout design rules and parasitic extraction engines.

AIDA assists expert analog IC designers by automating the most time-consuming and repetitive tasks from the typical analog IC design flow. AIDA-C automates circuit sizing with high accuracy and within a reduced time frame. AIDA-L generates the complete layout for sized circuits, from device placement to detailed routing.

Analog and Mixed-Signal (AMS) systems are found in a wide range of applications, such as, communications, medical or multimedia applications. These extremely competitive markets force the analog designer to face the complex design challenges within strict and demanding timeframes. Today's analog design is supported by circuit simulators, layout editing environments and verification tools, however the design cycle for AMS ICs is still long and error-prone.

AIDA's framework targets the analog IC design automation while keeping the common design flow by involving the designer and his(her) knowledge and focusing on efficiently automating repetitive design tasks. Thus, facilitating design reuse and fast response to specification changes of analog cells like VCO, LNA, voltage mixer, differential amplifiers, band gap voltage references, integrators, comparators, etc..

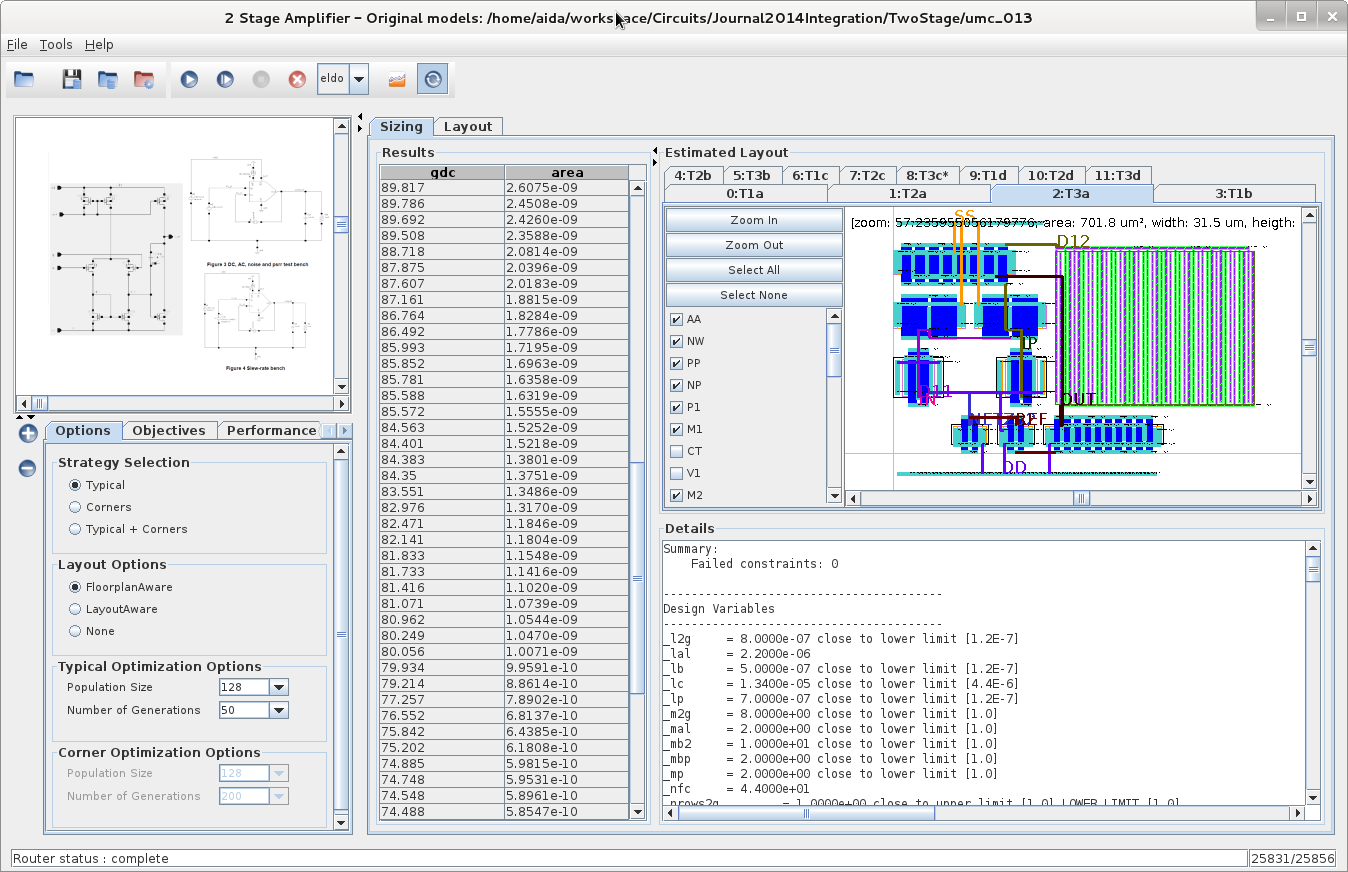

AIDA framework is composed by two main modules: AIDA-C and AIDA-L. AIDA also includes an intuitive GUI allowing the designer to manage and interact with the design automation process.

| AIDA’s Graphical User Interface navigating the sizing solution set and showing the corresponding floorplan and global routing. |

|